## PURE SOUND

Building a Straight Wire to the Soul of Music

# EVAL9 USER'S GUIDE

| 1 | 1 Introduction                                      | 2      |

|---|-----------------------------------------------------|--------|

|   | 1.1 Usage and Purpose                               | 2      |

|   | 1.1.1 Setup and operation                           | 2      |

|   | 1.1.2 Power Testing                                 | 2      |

| 2 | 2 EVAL9 Overview                                    | 3      |

| 3 | 3 Interface                                         | 4      |

|   | 3.1 I2C connector, J1                               | 4      |

|   | 3.2 Power connector, J2                             | 4      |

|   | 3.3 Aux connector, J3                               | 4      |

|   | 3.4 Analog input XLR connectors, J5 & J10           |        |

|   | 3.5 Edge connectors, J200_A1 & J200_A2              | 6      |

|   | 3.6 Speaker output connectors, J4, J7, J14 & J9     |        |

|   | 3.7 Gain-select jumpers, J100_B1 & J100_B2          | 7      |

|   | 3.8 BTL/SE jumper, J8                               | 9      |

| 4 | 4 Power Supplies                                    |        |

|   | 4.1 Linear Regulators                               |        |

| 5 | 5 Operating Modes & Status Reporting                |        |

|   | 5.1 Mode Configuration                              |        |

|   | 5.2 HW Mode                                         |        |

|   | 5.3 SW Model                                        |        |

| 6 | 6 Mechanical Specifications & System Considerations |        |

|   | 6.1 EVAL9 Dimensions                                |        |

|   | 6.2 Thermal Requirements                            |        |

|   | 6.3 Mechanical Requirements                         |        |

|   | 6.4 Compliance Testing                              |        |

|   | 7 External Standby Switch                           |        |

| 8 | 8 Revision History                                  | lb     |

| _ | E' 1 EVALO 0                                        | 7      |

|   | Figure 1: EVAL9 Overview                            |        |

|   | Figure 2: XLR to RCA wiring                         |        |

|   | Figure 3: Edge Connector pinout                     |        |

|   | Figure 4: Buffer schematic                          |        |

|   | Figure 5: BTL output configuration                  |        |

|   | Figure 7: Linear Regulator Schamatic                |        |

|   | Figure 9: Mode Selection                            |        |

|   | Figure 8: Mode Selection                            |        |

|   | Figure 9: Dimensions                                |        |

|   | Figure 10: Bottom-side mounting holes               |        |

|   |                                                     |        |

| Г | Figure 12: External Standby Switch                  | 10     |

| Т | Table 1: I2C connector, J1                          | 4      |

| Τ | Table 2: Power connector, J2                        | 4      |

| Τ | Table 3: Aux connector, J3                          | 4      |

|   |                                                     |        |

|   | Table 4: Analog input XLR connectors, J5 & J10      |        |

| Τ | Table 5: Edge Connectors, J200_A1 & J200_A23        |        |

|   |                                                     | 6      |

| Τ | Table 5: Edge Connectors, J200_A1 & J200_A23        | 6<br>7 |

| Table 9: Recommended Supply Voltages | 10  |

|--------------------------------------|-----|

| Table 10 Mode Selection              | .12 |

| Table 11: Revision History           | .16 |

## 1 Introduction

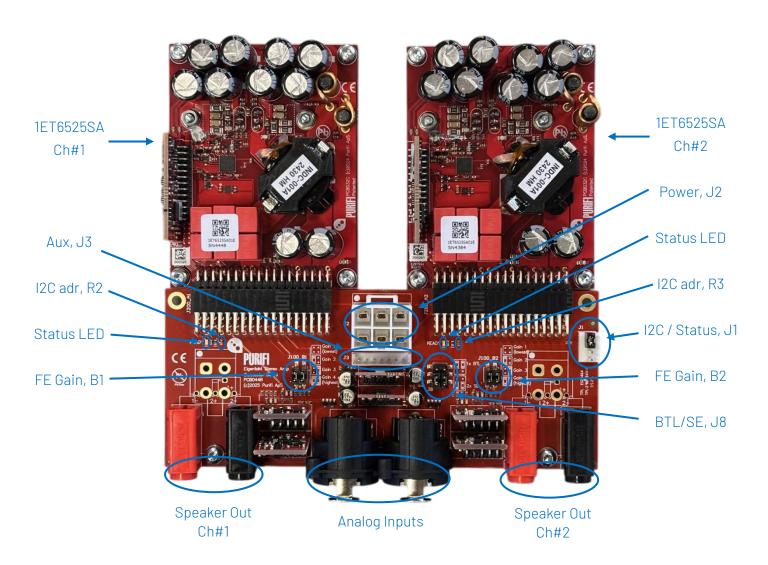

This document describes the operation, function and usage of the EVAL9 evaluation kit ("EVM") consisting of two 1ET6525SA amplifier modules and one FE08 deluxe stereo front-end module.

## 1.1 Usage and Purpose

The EVM is provided for engineering evaluation and laboratory test purposes only. Great care should be taken when handling the EVM, especially when connected to power supplies and loads. Observe the voltage and power ratings and apply suitable precautions to protect the operator from electrical hazards.

Also note that the EVM is provided as an unshielded PCB assembly and should be protected from ESD as well as mechanical stress.

## 1.1.1 Setup and operation

- 1. Plug 1ET6525SA modules into the Front-End Board (FE08)

- 2. Place EVM on a flat surface. Note that the amplifier base plates are connected to GND and should be attached to an external heatsink, e.g., a larger aluminum plate, for extended high power testing.

- 3. Connect external laboratory power supplies (or other suitable PSU's) to FE08 (refer to section 4)

- 4. Connect audio inputs and speakers (or other suitable loads/test equipment)

Two red LED's will light up when all supply voltages are within operational range.

- 5. It is recommended to disable operation (jumper) and turn off all power supplies when module is not in use

#### 1.1.2 Power Testing

The amplifier modules are protected from overheat via individual thermal protection systems that monitor the temperature of the aluminium base plates. The aluminium plates provide limited cooling, likely adequate for full-power music as well as typical test sweeps etc., However, continuous high-power operation requires additional cooling.

## 2 EVAL9 Overview

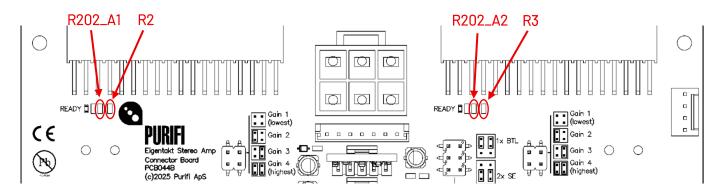

Figure 1: EVAL9 Overview

## 3 Interface

## 3.1 I2C connector, J1

| Pin | Signal | Rating | 1/0 | Description                                                                   |

|-----|--------|--------|-----|-------------------------------------------------------------------------------|

| 1   | PSUDIS |        | 0   | PSU off control signal (SW Mode), or                                          |

|     | /AMPON |        | 1   | Amplifier Disable (HW Mode) – pull low to enable Amp. HW mode is default (see |

|     |        |        |     | section 5.2)                                                                  |

| 2   | GND    |        | -   | Ground                                                                        |

| 7   | SCL    |        |     | I2C clock (SW Mode), or                                                       |

| J   | /FATAL |        | 0   | Amplifier "error/fail" (HW Mode) – signal goes low on error                   |

| /.  | SDA    |        | Ī   | I2C Data (SW Mode), or                                                        |

| 4   | READY  |        | 0   | Amplifier Ready (HW Mode) – "all good for operation" when high                |

Table 1: I2C connector, J1

Note: HW mode is enabled by default. For mode configuration see section 5.1.

Connector type: Molex: 0022232042.

## 3.2 Power connector, J2

| Pin | Signal | Rating | 1/0 | Description                          |

|-----|--------|--------|-----|--------------------------------------|

| 1   | VDR    |        | Р   | Gate Drive Supply, referenced to -VP |

| 2   | +VP    |        | Р   | Power Stage Supply, positive rail    |

| 3,6 | GND    |        | -   | Ground                               |

| 4,5 | -VP    |        | Р   | Power Stage Supply, negative rail    |

Table 2: Power connector, J2

Connector type equivalent: JST: B06P-VL. Matching cable part: JST: VLP-06V.

#### 3.3 Aux connector, J3

| Pin | Signal                                          | Rating | 1/0                                  | Description                                                    |

|-----|-------------------------------------------------|--------|--------------------------------------|----------------------------------------------------------------|

| 1   | , PSUDIS 0 PSU off control signal (SW Mode), or |        | PSU off control signal (SW Mode), or |                                                                |

| I   | /AMPON                                          |        | 1                                    | Amplifier Disable (HW Mode) – pull low to enable Amp           |

| 2   | SDA                                             |        | 1                                    | I2C Data (SW Mode), or                                         |

|     | READY                                           |        | 0                                    | Amplifier Ready (HW Mode) – "all good for operation" when high |

| 7   | SCL                                             |        | - 1                                  | I2C clock (SW Mode), or                                        |

| 3   | /FATAL                                          |        | 0                                    | Amplifier "error/fail" (HW Mode) – signal goes low on error    |

| 4   | +VSBY                                           |        | Р                                    | 5V feed-through from external PSU                              |

| 5   | +VUNREG                                         |        | Р                                    | Voltage regulator input, positive rail                         |

| 6   | GND                                             |        | -                                    | Ground                                                         |

| 7   | -VUNREG                                         |        | Р                                    | Voltage regulator input, negative rail                         |

Table 3: Aux connector, J3

Connector type: JST: B7B-EH-A(LF)(SN).

Matching cable part: JST: EHR-7.

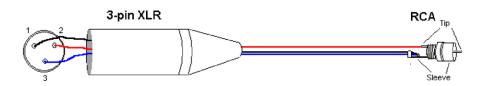

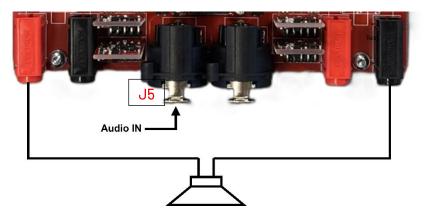

## 3.4 Analog input XLR connectors, J5 & J10

| Pin | Signal | Rating | 1/0 | Description            |

|-----|--------|--------|-----|------------------------|

| 1   | GND    |        | -   | Ground                 |

| 2   | IN+    |        |     | Analog input, positive |

| 3   | IN-    |        | Ī   | Analog input, negative |

Table 4: Analog input XLR connectors, J5 & J10

Connector type: Neutrik NC3FAAH2.

If a single-ended input is required, connect GND and IN- to the negative analog input. It is recommended to make this connection at the source end.

Figure 2: XLR to RCA wiring

## 3.5 Edge connectors, J200\_A1 & J200\_A2

| Pin                   | Signal  | Rating | 1/0                                                            | Description                                                               |

|-----------------------|---------|--------|----------------------------------------------------------------|---------------------------------------------------------------------------|

| Power Supplies        | 3       |        |                                                                |                                                                           |

| 1,2, 3, 4, 7 +VP      |         | Р      | Power Stage Supply, positive rail                              |                                                                           |

| 5, 6, 8, 9, 11, 12,   |         |        |                                                                |                                                                           |

| 37, 40, 41, 43,       | GND     |        | -                                                              | Ground                                                                    |

| 46, 49, 52            |         |        |                                                                |                                                                           |

| 10, 13, 14, 15, 16    | -VP     |        | Р                                                              | Power Stage Supply, negative rail                                         |

| 17                    | VDR     |        | Р                                                              | Gate Drive Supply, referenced to -VP                                      |

| 18                    | +VSBY   |        | Р                                                              | (optional use) External Voltage supply to amplifier module's 5V regulator |

| 38                    | GND     |        | -                                                              | Ground                                                                    |

| 39                    | -VOP    |        | Р                                                              | OPAMPs, negative rail                                                     |

| 17                    | +VOP    |        | Р                                                              | OPAMPs, positive rail                                                     |

| I/0's                 |         |        |                                                                |                                                                           |

| 19, 20, 21,           |         |        |                                                                |                                                                           |

| 22, 23, 24, 25,       | OUT-    |        | 0                                                              | Speaker Output, negative (internally connected to GND)                    |

| 26, 27<br>28, 29, 30, |         |        |                                                                |                                                                           |

| 31, 32, 33, 34,       | OUT+    |        | 0                                                              | Speaker Output, positive                                                  |

| 35, 36                | 0011    |        | U                                                              | Speaker output, positive                                                  |

| 42, 50, 51            | NC      |        | -                                                              | Not connected                                                             |

| 44                    | IN+     |        |                                                                | Analog Input, positive                                                    |

| 45                    | IN-     |        | 1                                                              | Analog Input, negative                                                    |

| 47                    | HS/ADDR |        | ı                                                              | Mode/I2C Address Selection; set by one 1% resistor.                       |

|                       | PSUDIS  |        | 0                                                              | PSU off control signal (SW Mode), or                                      |

| 48                    | /AMPON  |        | İ                                                              | Amplifier Disable (HW Mode) – pull low to enable Amp                      |

| F.7                   | SDA     |        | I                                                              | I2C Data (SW Mode), or                                                    |

| 53 READY              |         | 0      | Amplifier Ready (HW Mode) – "all good for operation" when high |                                                                           |

| F./                   | SCL     |        | -                                                              | I2C clock (SW Mode), or                                                   |

| 54                    | /FATAL  |        | 0                                                              | Amplifier "error/fail" (HW Mode) – signal goes low on error               |

Table 5: Edge Connectors, J200\_A1 & J200\_A23

Connector type: Samtec: SSW-118-02-T-T-RA

| 1 |     | 4   | 7   | 10  | 13  | 16    | 19   | 22   | 25   | 28   | 31   | 34   | 37   | 40  | 43  | 46     | 49  | 52  |

|---|-----|-----|-----|-----|-----|-------|------|------|------|------|------|------|------|-----|-----|--------|-----|-----|

|   | +VP | +VP | +VP | -VP | -VP | -VP   | OUT- | OUT- | OUT- | OUT+ | 0UT+ | 0UT+ | GND  | GND | GND | GND    | GND | GND |

| 2 | !   | 5   | 8   | 11  | 14  | 17    | 20   | 23   | 26   | 29   | 32   | 35   | 38   | 41  | 44  | 47     | 50  | 53  |

|   | +VP | GND | GND | GND | -VP | VDR   | OUT- | OUT- | OUT- | OUT+ | 0UT+ | 0UT+ | -VOP | GND | IN+ | ADDR   | NC  | SDA |

| 3 | i   | 6   | 9   | 12  | 15  | 18    | 21   | 24   | 27   | 30   | 33   | 36   | 39   | 42  | 45  | 48     | 51  | 54  |

|   | +VP | GND | GND | GND | -VP | +VSBY | OUT- | OUT- | OUT- | OUT+ | 0UT+ | 0UT+ | +VOP | NC  | IN- | /AMPON | NC  | SCL |

Figure 3: Edge Connector pinout

Note: Care should be taken to only connect the 1ET6525SA to the two lowest rows of pins.

## 3.6 Speaker output connectors, J4, J7, J14 & J9

| Pin | Signal | Rating | 1/0 | Description                          |

|-----|--------|--------|-----|--------------------------------------|

| J4  | OUT+   |        | 0   | Speaker output, positive - Channel 1 |

| J7  | OUT-   |        | 0   | Speaker output, negative – Channel 1 |

| J14 | OUT+   |        | 0   | Speaker output, positive – Channel 2 |

| J9  | OUT-   |        | 0   | Speaker output, negative – Channel 2 |

Table 6: Speaker output connectors, J4, J7, J14, J9

Connector: High current banana socket: Deltron: 571-0100(Black), 571-0500(Red)

## $3.7~Gain\text{-select jumpers, } J100\_B1 \& J100\_B2$

FE08 includes a pre-gain stage with four selectable settings. The gain can be set by placing jumpers as shown below:

| Description    | Gain 1(lowest) | Gain 2  | Gain 3  | Gain 4 (highest) |

|----------------|----------------|---------|---------|------------------|

| Front-End gain | 3 dB           | 11.6 dB | 13.7 dB | 17.2 dB          |

| Total EVM gain | 15.3 dB        | 23.9 dB | 26.0 dB | 29.5 dB          |

| Jumper setting |                |         |         |                  |

Table 7: Gain jumpers, B1 & B2

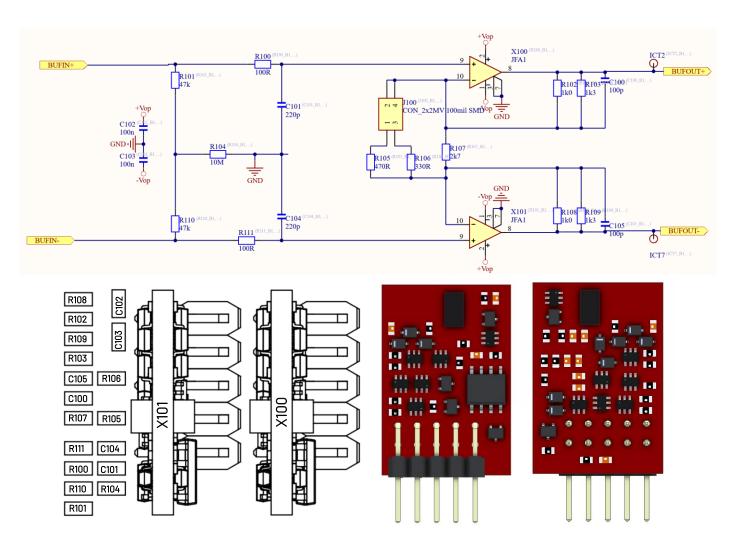

The pre-gain stage uses PURIFI's discrete op-amp **JFA1**, configured as balanced/single-ended to balanced gain stage as shown below:

Figure 4: Buffer schematic

Differential input impedance is 94.0 kohm.

## 3.8 BTL/SE jumper, J8

FE08 supports 1x BTL (bridged) or 2x SE (single-ended) operation. The mode can be chosen by placing the jumpers as shown below.

| Description    | 1x BTL | 2x SE |

|----------------|--------|-------|

| Jumper setting | 1x BTL | 2x SE |

Table 8: BTL/SE jumper, J8

Connector J5 serves as the input for BTL operation. In this mode, the amplifier outputs CH1(+) and CH2(-) are used to drive a single load. This configuration provides 2x higher output voltage swing and 4x increased power compared to single-ended mode. Note in BTL mode nominal load changes to 8ohm, and it will be current limited in 4ohm load.

Connect the speaker only between CH1(+) and CH2(-) as shown below.

Figure 5: BTL output configuration

WARNING - BTL mode: High voltage of up to 130V between CH1(+) and CH2(-). Do not touch these terminals.

sales@purifi-audio.com PURIFI Information (1.10) Nov 2025

## 4 Power Supplies

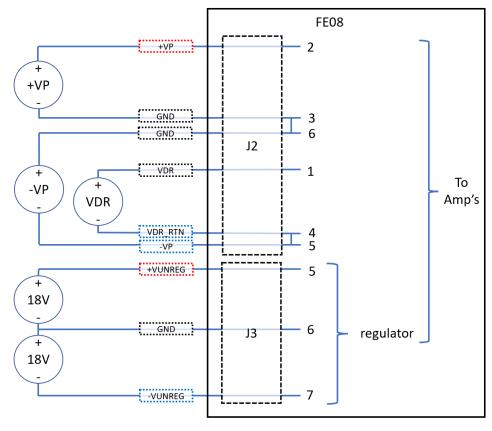

The figure below shows the required power supplies and how to connect these to FE08:

Figure 6: Power Supplies

All supplies levels should be cross-checked with the Recommended Operation Conditions as specified in the respective amplifier module data sheet.

Recommended supply voltages for EVAL9 (please also refer to the 1ET6525SA Data Sheet):

|            | Parameter                                       | Min  | Тур | Max   | Unit |  |  |  |  |  |  |

|------------|-------------------------------------------------|------|-----|-------|------|--|--|--|--|--|--|

| Power Supp | Power Supplies                                  |      |     |       |      |  |  |  |  |  |  |

| +VP        | Power Stage, positive rail voltage              | 32   | 65  | 70    | V    |  |  |  |  |  |  |

| -VP        | Power Stage, negative rail voltage              | -70  | -65 | -32   | V    |  |  |  |  |  |  |

| VDR        | Gate Drive, voltage (must be referenced to -VP) | 13.6 | 15  | 16.5  | V    |  |  |  |  |  |  |

| +VUNREG    | OPAMPs, positive rail voltage                   | 16.4 | 18  | 25    | V    |  |  |  |  |  |  |

| -VUNREG    | OPAMPs, negative rail voltage                   | -25  | -18 | -16.4 | V    |  |  |  |  |  |  |

Table 9: Recommended Supply Voltages

<u>sales@purifi-audio.com</u> PURIFI Information (1.10) Nov 2025 10

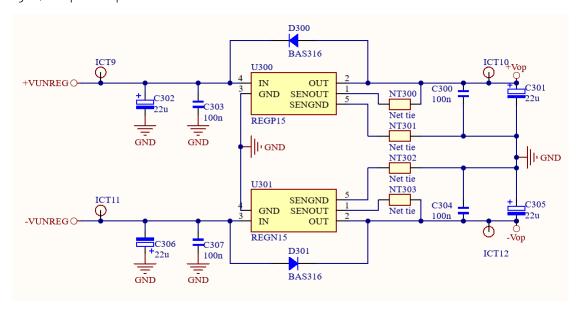

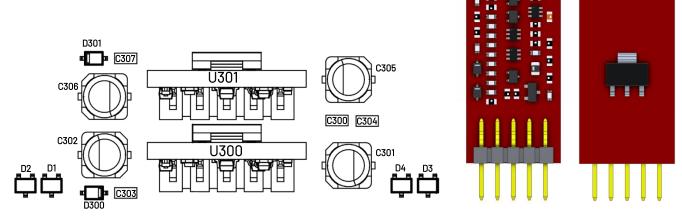

## 4.1 Linear Regulators

FE08 includes two low-noise, low-impedance discrete linear regulators for the OPAMP's negative and positive supply voltages, +Vop & -Vop. The schematic is shown here below:

Figure 7: Linear Regulator Schematic

## 5 Operating Modes & Status Reporting

## 5.1 Mode Configuration

The EVAL9 can operate in two modes:

- 1. HW Mode: all control and status via pins (HW interface) DEFAULT CONFIGUTATION

- 2. SW Mode: enables control and status via I2C interface

FE08 is configured for HW Mode by default. To reconfigure for SW Mode, at bit of soldering is required, see Table 10 and Figure 8:

| FP      | Channel | Description           | HW Mode | SW Mode             |

|---------|---------|-----------------------|---------|---------------------|

| R202_A1 | 1       | Mada Calaatian        | Diede   | 00 obust            |

| R202_A2 | 2       | Mode Selection        | Diode   | 0Ω shunt            |

| R2      | 1       | I2C Address Selection | 0       | Refer to data sheet |

| R3      | 2       | 12C Address Selection | Open    | Refer to data sheet |

Table 10 Mode Selection

Figure 8: Mode Selection

## 5.2 HW Mode

The amplifier modules are controlled via J3 which is connected to amplifier control signal /AMPON. /AMPON is also made available on connector J1 and can be controlled via external source.

Amplifier status is signaled via READY and /FATAL:

READY signals are connected to individual LED's on FE08.

/FATAL signals are wire OR'ed together on FE08 and pinned out on connectors: J1 and J3.

## 5.3 SW Model

The main feature of the SW Mode is access via I2C to status and control information. The I2C register map can be found in the amplifier data sheet.

I2C is accessed via SCL, SDA on connectors J1 and J3.

The I2C address can be programmed via value of resistors R2 and R3 on FE08. Refer to the **Mode Selection via HS/ADR** table in the amplifier data sheet for information on resistor value vs. I2C address.

sales@purifi-audio.com PURIFI Information (1.10) Nov 2025 12

## 6 Mechanical Specifications & System Considerations

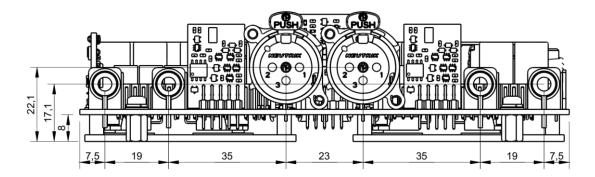

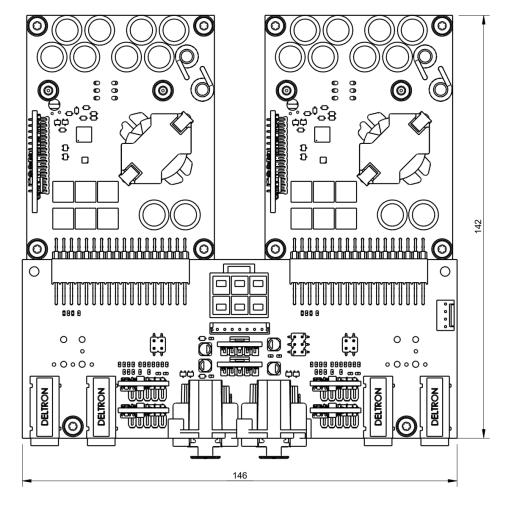

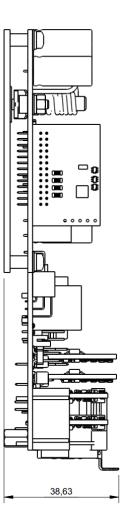

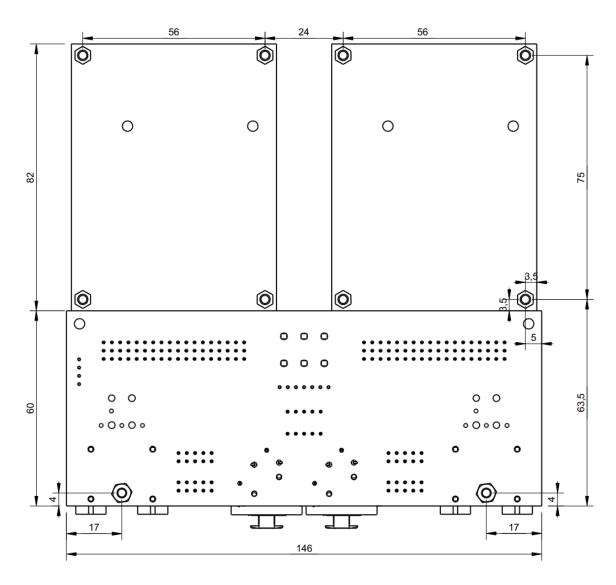

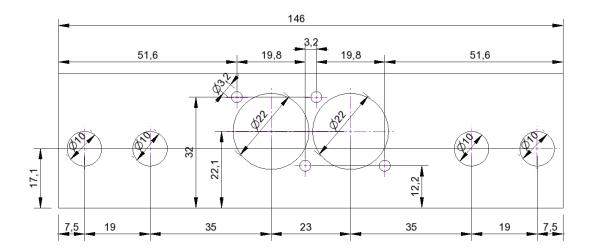

## 6.1 EVAL9 Dimensions

13

Figure 9: Dimensions

<u>sales@purifi-audio.com</u> PURIFI Information (1.10) Nov 2025

Figure 10: Bottom-side mounting holes

Figure 11: Back plate mounting holes

Note: Dimensions from bottom mounting plate include the 8mm standoff.

## 6.2 Thermal Requirements

While 1ET6525SA has very low idle losses and high overall efficiency, adequate cooling is essential for sustained power delivery. Careful consideration must be given to design the thermal system to achieve desired power specifications.

It is recommended to mount the module on a heatsink, e.g., an adequately designed aluminum chassis.

## 6.3 Mechanical Requirements

Related to mechanical robustness of the end application: It is the reasonability of the system integrator to specify process, materials, locations, etc. for e.g., gluing of critical components which may be required and to prove/document short- and long-term performance and reliability. The system integrator must ensure integrity of mounting methods and materials used related to fixation of the module. It is recommended to thoroughly test the final product for robustness against, e.g., shock and vibration.

## 6.4 Compliance Testing

1ET6525SA is designed with considerations for compliance of the end application. However, it is the responsibility of the system integrator to ensure any form of design-for-compliance and associated testing/certification which may be required.

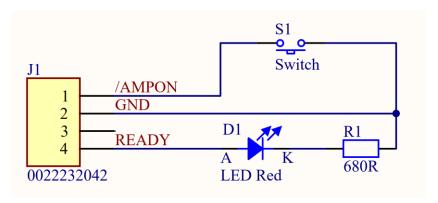

## 7 External Standby Switch

Standby is controlled by the /AMPON signal, which is available on J1 pin 1. J1 also includes a GND pin, allowing an external standby switch to be implemented by connecting a switch between pin 1 and pin 2 and removing the jumper from J1.

The FE08 board, in HW mode, includes two diodes that OR the READY signals from Ch1 and Ch2. An ON/OFF indicator can therefore be implemented by connecting an LED with a 680-ohm resistor between J1 pin 4 and J1 pin 2.

A wiring diagram example is shown below:

Figure 12: External Standby Switch

## 8 Revision History

| Rev    | Date       | Description                                         | ID  |

|--------|------------|-----------------------------------------------------|-----|

| (1.00) | 2025-10-31 | Initial Issue                                       | AJA |

| (1.10) | 2025-11-19 | Updated image and orientation for AUX Connector, J3 | AJA |

|        |            |                                                     |     |

|        |            |                                                     |     |

|        |            |                                                     |     |

|        |            |                                                     |     |

|        |            |                                                     |     |

Table 11: Revision History

sales@purifi-audio.com PURIFI Information (1.10) Nov 2025 16

#### 1 EVM Use Restrictions and Warnings:

1.1 EVMS ARE NOT FOR USE IN FUNCTIONAL SAFETY AND/OR SAFETY CRITICAL EVALUATIONS, INCLUDING BUT NOT LIMITED TO EVALUATIONS OF LIFE SUPPORT APPLICATIONS. 1.2 User must read and apply the user quide and other available documentation provided by PURIFI ApS regarding the EVM prior to handling or using the EVM. 1.3 Safety-Related Warnings and Restrictions: 1.3.1 User shall operate the EVM within PURIFI ApS's recommended specifications and environmental considerations stated in the specification or other available documentation provided by PURIFI APS, and any other applicable requirements and employ reasonable and customary safeguards. Exceeding the specified performance ratings and specifications (including but not limited to input and output voltage, current, power, and environmental ranges) for the EVM may cause personal injury or death, or property damage. Any loads applied outside of the specified output range may also result in unintended and/or inaccurate operation and/or possible permanent damage to the EVM and/or interface electronics. Please consult the EVM documentation prior to connecting any load to the EVM output. During normal operation, even with the inputs and outputs are kept within the specified allowable ranges, some circuit components may have elevated case temperatures. When working with the EVM, please be aware that the EVM may become very warm. If there is uncertainty as to the ratings and specifications, please contact PURIFI ApS prior to connecting interface electronics including input power and intended loads. 1.3.2 EVMs are intended solely for use by technically qualified, professional electronics experts who are familiar with the dangers and application risks associated with handling electrical mechanical components, systems, and subsystems. User assumes all responsibility and liability for proper and safe handling and use of the EVM by User or its employees, affiliates, contractors or designees. User assumes all responsibility and liability to ensure that any interfaces (electronic and/or mechanical) between the EVM and any human body are designed with suitable isolation and means to safely limit accessible leakage currents to minimize the risk of electrical shock hazard. User assumes all responsibility and liability for any improper or unsafe handling or use of the EVM by User or its employees, affiliates, contractors or designees. 1.4 User assumes all responsibility and liability to determine whether the EVM is subject to any applicable international, federal, state, or local laws and regulations related to User's handling and use of the EVM and, if applicable, User assumes all responsibility and liability for compliance in all respects with such laws and regulations. User assumes all responsibility and liability for proper disposal and recycling of the EVM consistent with all applicable international, federal, state, and local requirements.

- 2. Accuracy of Information: To the extent PURIFI ApS provides information on function of EVMs, PURIFI ApS attempts to be as accurate as possible. However, PURIFI ApS does not warrant the accuracy of EVM descriptions or other information on its websites as accurate, complete, reliable, current, or error-free.

- 3. Disclaimers: 3.1 EXCEPT AS SET FORTH ABOVE, EVMS AND ANY WRITTEN EVM MATERIALS PROVIDED WITH THE EVM (AND THE DESIGN OF THE EVM ITSELF) ARE PROVIDED "AS IS". PURIFI APS DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, REGARDING TO E.G. BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS. 3.2 EXCEPT FOR THE LIMITED RIGHT TO USE THE EVM SET FORTH HEREIN, NOTHING IN THESE TERMS AND CONDITIONS SHALL BE CONSTRUED AS GRANTING OR CONFERRING ANY RIGHTS BY LICENSE, PATENT, OR ANY OTHER INDUSTRIAL OR INTELLECTUAL PROPERTY RIGHT OF PURIFI APS, ITS SUPPLIERS/LICENSORS OR ANY OTHER THIRD PARTY, TO USE THE EVM IN ANY FINISHED END-USER OR READY-TO-USE FINAL PRODUCT, OR FOR ANY INVENTION, DISCOVERY OR IMPROVEMENT MADE, CONCEIVED OR ACQUIRED PRIOR TO OR AFTER DELIVERY OF THE EVM.

- 4. USER'S INDEMNITY OBLIGATIONS AND REPRESENTATIONS. USER WILL DEFEND, INDEMNIFY AND HOLD PURIFI APS, ITS LICENSORS AND THEIR REPRESENTATIVES HARMLESS FROM AND AGAINST ANY AND ALL CLAIMS, DAMAGES, LOSSES, EXPENSES, COSTS AND LIABILITIES (COLLECTIVELY, "CLAIMS") ARISING OUT OF OR IN CONNECTION WITH ANY HANDLING OR USE OF THE EVM THAT IS NOT IN ACCORDANCE WITH THESE TERMS AND CONDITIONS. THIS OBLIGATION SHALL APPLY WHETHER CLAIMS ARISE UNDER STATUTE, REGULATION, OR LAW OF TORT, CONTRACT OR ANY OTHER LAW, AND EVEN IF THE EVM FAILS TO PERFORM AS DESCRIBED OR EXPECTED.

- 5. Limitations on Damages and Liability: 5.1 General Limitations. IN NO EVENT SHALL PURIFI APS BE LIABLE FOR ANY SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL, OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF THESE TERMS AND CONDITIONS OR THE USE OF THE EVMS PROVIDED HEREUNDER, REGARDLESS OF WHETHER PURIFI APS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. EXCLUDED DAMAGES INCLUDE, BUT ARE NOT LIMITED TO, COST OF REMOVAL OR REINSTALLATION, ANCILLARY COSTS TO THE PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES, RETESTING, OUTSIDE COMPUTER TIME, LABOR COSTS, LOSS OF GOODWILL, LOSS OF PROFITS, LOSS OF SAVINGS, LOSS OF USE, LOSS OF DATA, OR BUSINESS INTERRUPTION. NO CLAIM, SUIT OR ACTION SHALL BE BROUGHT AGAINST PURIFI APS MORE THAN ONE YEAR AFTER THE RELATED INCIDENCE HAS OCCURRED.

- 5.2 Specific Limitations. IN NO EVENT SHALL PURIFI APS'S AGGREGATE LIABILITY FROM ANY WARRANTY OR OTHER OBLIGATION ARISING OUT OF OR IN CONNECTION WITH THESE TERMS AND CONDITIONS, OR ANY USE OF ANY PURIFI APS EVM PROVIDED HEREUNDER, EXCEED THE TOTAL AMOUNT PAID TO PURIFI APS FOR THE PARTICULAR UNITS SOLD UNDER THESE TERMS AND CONDITIONS WITH RESPECT TO WHICH LOSSES OR DAMAGES ARE CLAIMED. THE EXISTENCE OF MORE THAN ONE CLAIM AGAINST THE PARTICULAR UNITS SOLD TO USER UNDER THESE TERMS AND CONDITIONS SHALL NOT ENLARGE OR EXTEND THIS LIMIT.

- 6. Governing Law: These terms and conditions shall be governed by and interpreted in accordance with the laws of Denmark, excluding Denmark's conflict-of-law rules, leading to the use of other law than the laws of Denmark. User agrees that non-exclusive jurisdiction for any dispute arising out of or relating to these terms and conditions lies within the courts of Denmark and consents to venue in Copenhagen, Denmark. Notwithstanding the foregoing, any judgment may be enforced in Danish court, and PURIFI ApS may seek injunctive relief in Denmark or foreign countries.

sales@purifi-audio.com PURIFI Information (1.10) Nov 2025 17