# PURE SOUND

Building a Straight Wire to the Soul of Music

# **KEY SPECIFICATIONS**

- 2<sup>nd</sup> Generation EIGENTAKT

- Single-channel, analog-input Class D amplifier module

- Negligible THD and IMD

- Extraordinarily Low Noise

- Load-invariant Response

- Exceptionally Clean Clipping

- Low Losses & High Efficiency

| Output Power               | >450W @ 1% THD, 4Ω                     |

|----------------------------|----------------------------------------|

| Output Current             | ~25A                                   |

| THD+N                      | <0.0001% (-120dB) @ 100W, 4Ω, 20-20kHz |

| Dynamic Range              | ~137dB(A)                              |

| Output Noise               | ~6.6µV(A)                              |

| Gain                       | 12.3dB                                 |

| Output Impedance           | <30μΩ @ 1kHz                           |

| Efficiency                 | >94%                                   |

| Idle losses (output stage) | ~1.6W                                  |

| Supply                     | ±32V to ±65V DC                        |

| Size                       | 82x63x33mm                             |

# 1ET6525SA - Data Sheet

| 1 | Specifications                                                 | 3    |

|---|----------------------------------------------------------------|------|

|   | 1.1 Absolute Maximum Ratings                                   |      |

|   | 1.2 Recommended Operating Conditions                           | 3    |

|   | 1.3 Audio Characteristics                                      | 4    |

|   | 1.4 Typical Audio Performance, Graphs                          | 5    |

|   | 1.5 Electrical Characteristics                                 | 8    |

|   | 1.6 Timing Characteristics                                     | 9    |

|   | 1.7 Mechanical Characteristics                                 | 9    |

| 2 | Introduction                                                   | . 10 |

| 3 | Overview                                                       | 11   |

|   | 3.1 Edge Connector, J3                                         |      |

| 4 | Power Supply, Control Signals & I/O's                          | 12   |

|   | 4.1 Power Supply                                               |      |

|   | 4.1.1 Power Stage Supply (+VP, -VP)                            | 12   |

|   | 4.1.2 Gate Drive Supply (VDR)                                  | 13   |

|   | 4.1.3 OPAMPs Supply (+VOP, -VOP)                               |      |

|   | 4.1.4 (optional) Digital Supply (VD)                           | 13   |

|   | 4.1.5 Power Supply Sequencing                                  | 13   |

|   | 4.2 Control Signals                                            |      |

|   | 4.2.1 PSUDIS & /AMPON                                          |      |

|   | 4.2.2 SCL & /FATAL                                             |      |

|   | 4.2.3 SDA & READY                                              |      |

|   | 4.3 Audio Inputs & Output                                      |      |

|   | 4.3.1 Audio Input (IN+, IN-)                                   |      |

|   | 4.3.2 Speaker Output (OUT+, OUT-)                              |      |

| 5 | Operating Modes & Status Reporting                             |      |

|   | 5.1 Mode Selection (HS/ADDR Settings)                          |      |

|   | 5.2 HW Modes                                                   |      |

|   | 5.3 SW Mode                                                    |      |

|   | 5.3.1 PSUDIS (GPIO)                                            |      |

|   | 5.4 I2C Register Map                                           |      |

| 6 | Protection System                                              |      |

|   | 6.1 Environmental checks                                       |      |

|   | 6.1.1 Over/Under-Voltage Protection, +VP, -VP, VDR, +VOP, -VOP |      |

|   | 6.1.2 Temperature Protection, Backplate                        |      |

|   | 6.2 Overcurrent Protection (OCP)                               |      |

|   | 6.3 Overload Protection (OLP)                                  |      |

| _ | 6.4 DC Protection (DCP)                                        |      |

| 7 | Mechanical Specifications & System Considerations              |      |

|   | 7.1 Module Dimensions                                          |      |

|   | 7.2 Thermal Requirements                                       |      |

|   | 7.3 Mechanical Requirements                                    |      |

| 0 | 7.4 Compliance Testing                                         |      |

| 8 | Revision History                                               | . 23 |

# 1ET6525SA - Data Sheet

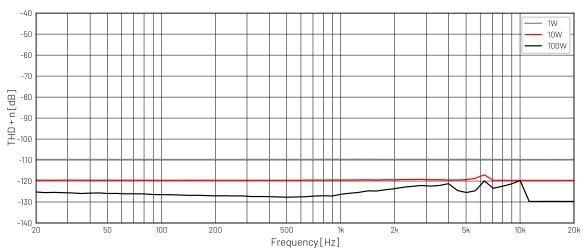

| Figure 1 THD [dB] vs. Frequency @ 4 $\Omega$              | 5  |

|-----------------------------------------------------------|----|

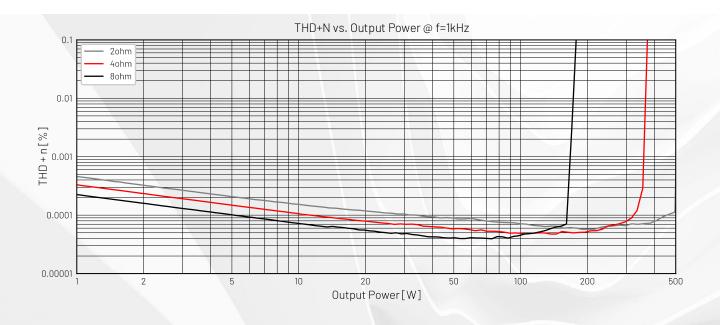

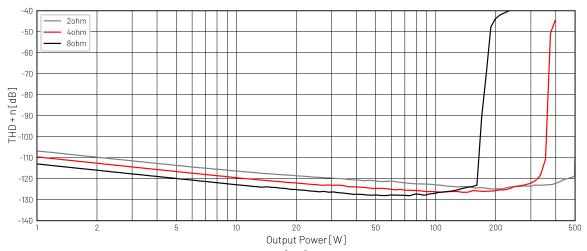

| Figure 2 THD+N [dB] vs. Power @ f=1kHz                    | 5  |

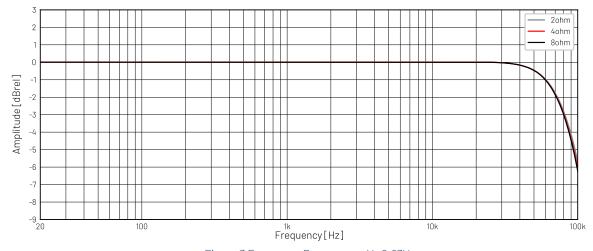

| Figure 3 Frequency Response @ V <sub>i</sub> =2.83V       | 5  |

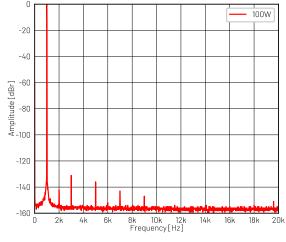

| Figure 4 Frequency Spectrum (FFT) @ 1kHz, 1W, 4Ω          | 6  |

| Figure 5 Intermodulation Distortion @ 18+19kHz, 1W, 4Ω    | 6  |

| Figure 6 Frequency Spectrum (FFT) @ 1kHz, 10W, 4Ω         | 6  |

| Figure 7 Intermodulation Distortion @ 18+19kHz, 10W, 4Ω   | 6  |

| Figure 8 Frequency Spectrum (FFT) @ 1kHz, 100W, 4Ω        | 6  |

| Figure 9 Intermodulation Distortion @ 18+19kHz, 100W, 4Ω  |    |

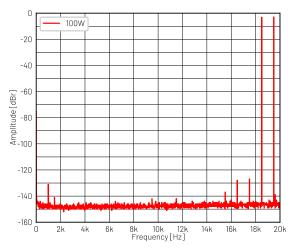

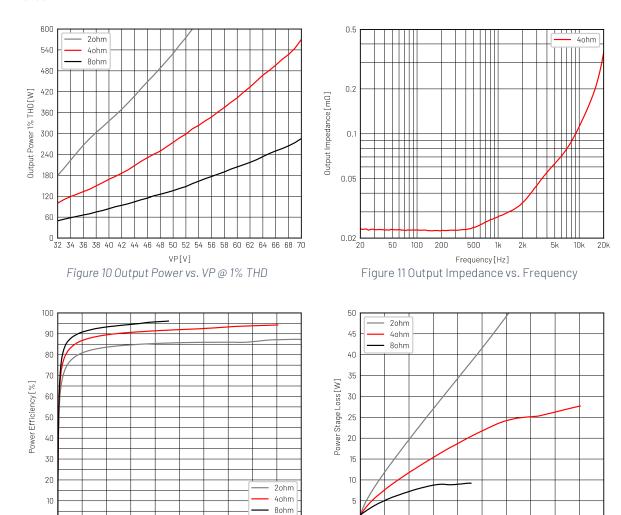

| Figure 10 Output Power vs. VP @ 1% THD                    | 7  |

| Figure 11 Output Impedance vs. Frequency                  |    |

| Figure 12 Power Stage Efficiency vs. Output Power         | 7  |

| Figure 13 Power Stage Loss vs. Output Power (one channel) | 7  |

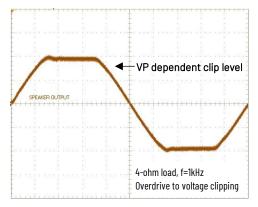

| Figure 14 Voltage Clipping/Recovery (behavior)            |    |

| Figure 15 Current Clipping/Recovery (behavior)            | 7  |

| Figure 16 1ET6525SA top view                              | 11 |

| Figure 17 Power Supplies                                  | 12 |

| Figure 18 Dimensions                                      | 22 |

|                                                           |    |

| Table 1 Absolute Maximum Ratings                          |    |

| Table 2 Recommended Operating Conditions                  |    |

| Table 3 Audio Characteristics                             |    |

| Table 4 Electrical Characteristics                        |    |

| Table 5 Timing Characteristics                            |    |

| Table 6 Mechanical Characteristics                        |    |

| Table 7 Edge Connector, J3                                |    |

| Table 8 Mode Selection via HS/ADDR                        |    |

| Table 9 Status/Control signals in HW Mode                 |    |

| Table 10 Status/Control signals in SW Mode                |    |

| Table 11 PSUDIS (GPIO) mapping                            |    |

| Table 12 I2C Register Map                                 |    |

| Table 13 Revision History                                 | 23 |

# 1 Specifications

# 1.1 Absolute Maximum Ratings

Referenced to GND unless otherwise noted.

|          | Parameter                                            | Min                         | Max  | Unit |    |

|----------|------------------------------------------------------|-----------------------------|------|------|----|

|          | Power Stage Supply, positive rail voltage (+VP)      | -0.3                        | 75   | V    |    |

|          | Power Stage Supply, negative rail voltage (-VP)      |                             | -75  | 0.3  | V  |

| Power    | Gate Drive Supply, voltage, referenced to -VP(VDR)   |                             | -0.3 | 20   | V  |

| Supplies | OPAMPs supply, positive rail voltage (+VOP)          |                             | -0.3 | 20   | V  |

|          | OPAMPs supply, negative rail voltage (-VOP)          | -20                         | 0.3  | V    |    |

|          | Digital Supply, voltage (VD) (optional use)          | -0.3                        | 20   | V    |    |

|          | Analog Inputs (+AIN, -AIN)                           | -15                         | 15   | V    |    |

|          | Logic-level outputs, continuous current (SMPS_OFF,   |                             | 50   | mΑ   |    |

| I/0's    | Logic-level inputs, voltage (/AMPON, SDA, SCL,       |                             | -0.3 | 5.3  | V  |

|          | /FATAL)                                              | +VOP < 5.5V, 0V < VD < 5.5V | -0.3 | VD   | V  |

|          | Open-drain, bi-directional, continuous current (SDA) |                             |      | 50   | mΑ |

|          | Ambient temperature                                  |                             |      | 100  | °C |

| Env.     | Heatsink temperature                                 |                             |      | 100  | °C |

|          | Relative Humidity, non-condensing                    |                             | 85   | %    |    |

Stress beyond Absolute Maximum Ratings may cause permanent damage to the Design and associated circuitry. Attempts to operate the Design within Absolute Maximum Rating but outside Recommended Operation Conditions (Table 2) may result in non-functional circuits and erroneous behavior.

Table 1 Absolute Maximum Ratings

# 1.2 Recommended Operating Conditions

Amplifier operation is permitted only under conditions stated in Table 2.

Referenced to GND unless otherwise noted.

|                        | Parameter                                                                  | Min   | Typ <sup>1)</sup>      | Max   | Unit |

|------------------------|----------------------------------------------------------------------------|-------|------------------------|-------|------|

| Power Sup              | pplies                                                                     |       |                        |       |      |

| +VP                    | Power Stage, positive rail voltage                                         | 32    | 65                     | 70    | V    |

| -VP                    | Power Stage, negative rail voltage                                         | -70   | -65                    | -32   | V    |

| VDR                    | Gate Drive, voltage (must be referenced to -VP)                            | 13.6  | 15                     | 16.5  | V    |

| +VOP                   | OPAMPs, positive rail voltage                                              | 11.4  | 12                     | 16.5  | V    |

| -VOP                   | OPAMPs, negative rail voltage                                              | -16.5 | -12                    | -11.4 | V    |

| VD                     | Digital, voltage (optional use)                                            | 4     | 5                      | 16.5  | V    |

| I/0's                  |                                                                            |       |                        |       |      |

| V <sub>in_dif</sub>    | Analog Inputs, differential rms voltage (pos. to neg. input) <sup>2)</sup> | -15.5 |                        | 15.5  | V    |

| $V_{in\_cm}$           | Analog Inputs, common-mode voltage                                         | -5    | 0                      | 5     | V    |

| R∟                     | Speaker Load, resistive                                                    | 23)   | 4                      | ∞     | Ω    |

| ZL                     | Speaker Load, capacitive                                                   |       | 0                      | 1     | μF   |

| Environm               | ental                                                                      |       |                        |       |      |

| TA                     | Ambient temperature                                                        | 0     | 25                     | 60    | °C   |

| T <sub>HS</sub>        | Heatsink temperature                                                       | 0     | 25                     | 75    | °C   |

| $\theta_{\text{HS-A}}$ | Thermal resistance, Heatsink to Ambient                                    |       | see note <sup>47</sup> | )     | °C/W |

| RH                     | Humidity, relative (non-condensing)                                        |       | 50                     | 85    | %    |

<sup>1)</sup> Audio Performance Specs are not guaranteed outside Typ. recommended operating conditions.

Table 2 Recommended Operating Conditions

sales@purifi-audio.com (1.00) December 2024

<sup>2) +/-15</sup>Vpeak corresponds to approximately full rated power (1% THD) in typ. load condition

<sup>3)</sup> The amplifier is stable into loads  $<2\Omega$ . Output power into impedances  $<3.2~\Omega$  may be limited by the Over Current Protection system.

<sup>4)</sup> The required  $\theta_{HS-A}$  depends highly on the desired sustained power delivery specification – see section 7.2)

## 1.3 Audio Characteristics

$R_L=4\Omega$ ,  $T_A=25^{\circ}$  free operating air, f=1kHz, 20kHz AES17 filter (AP), typical operating conditions (Table 2) unless otherwise noted.

|            | Parameter                               | Conditions                                     | Min Typ Max           | Unit |

|------------|-----------------------------------------|------------------------------------------------|-----------------------|------|

|            |                                         | R <sub>L</sub> = 8Ω, 1%THD                     | 230                   | W    |

|            | Output Power, Short term                | $R_L = 4\Omega$ , 1%THD                        | 450                   | W    |

| $P_0$      |                                         | R <sub>L</sub> = 2Ω, 1%THD                     | 510 <sup>1)</sup>     | W    |

|            | Output Power, Continuous <sup>2)</sup>  | _                                              | (as limited by        | _    |

|            | output Fower, continuous                |                                                | thermal system)       |      |

|            |                                         | P <sub>0</sub> =1W, f=1kHz                     | 0.00035               | %    |

|            |                                         | P <sub>0</sub> =10W, f=1kHz                    | 0.0001                | %    |

| THD+N      | Total Harmonic Distortion + Noise       | P <sub>0</sub> =100W, f=1kHz                   | 0.00005 <sup>3)</sup> | %    |

| 1110.11    | Total Harmonic Distortion - Noise       | P <sub>0</sub> =1W, f=20-20kHz                 | 0.00035               | %    |

|            |                                         | P <sub>0</sub> =10W, f=20-20kHz                | 0.00029               | %    |

|            |                                         | P <sub>0</sub> =100W, f=20-20kHz               | 0.0001 <sup>3)</sup>  | %    |

|            |                                         | P <sub>0</sub> =1W, f=18.5kHz+19.5kHz          | 0.000003              | %    |

|            | Intermodulation Distortion, CCIF        | P <sub>0</sub> =10W, f=18.5kHz+19.5kHz         | 0.000006              | %    |

| IMD        |                                         | P <sub>0</sub> =100W, f=18.5kHz+19.5kHz        | 0.000005              | %    |

| IMD        | Dynamic Intermodulation Distortion, DIM | P <sub>0</sub> =1W, DIM30                      | 0.002 <sup>3)</sup>   | %    |

|            |                                         | P <sub>0</sub> =10W, DIM30                     | 0.002 <sup>3)</sup>   | %    |

|            |                                         | P <sub>0</sub> =100W, DIM30                    | 0.009 <sup>3)</sup>   | %    |

| ICN        | Idle Noise, speaker output              | A-weighted                                     | 6.6                   | μV   |

| DNR        | Dynamic Range                           | A-weighted, relative 450W, R <sub>L</sub> = 4Ω | 137                   | dB   |

| SNR        | Signal to Noise Ratio                   | A-weighted, relative to 450W, $R_L = 4\Omega$  | 137                   | dB   |

|            |                                         | $R_L = 8\Omega$ , $V_o = 2.83V@1kHz(=1W)$      | 80/100                | kHz  |

|            | Frequency Response, upper -3dB/-6dB     | R <sub>L</sub> =4Ω, V₀=2.83V@1kHz              | 80/100                | kHz  |

|            |                                         | $R_L = 2\Omega$ , $V_o = 2.83V@1kHz$           | 80/100                | kHz  |

|            | Frequency Response, lower -3dB          | -                                              | (DC coupled)          | -    |

| BW         |                                         | $R_L = 8\Omega$ , $f = 20-20$ kHz              | ±0.01                 | dB   |

|            | Frequency Response, flatness            | $R_L = 4\Omega$ , $f = 20-20$ kHz              | ±0.01                 | dB   |

|            | Trequency Nesponse, namess              | $R_L = 2\Omega$ , $f = 20-20$ kHz              | ±0.01                 | dB   |

|            |                                         | $R_L = \infty \Omega$ , $f = 20-20$ kHz        | ±0.01                 | dB   |

|            | Frequency Response, load variation      | $R_L = 2 - \infty \Omega$ , f= 20-20kHz        | ±0.01                 | dB   |

| Zo         | Output Impedance <sup>4)</sup>          | 1kHz, I <sub>out</sub> =1A                     | 0.03                  | mΩ   |

| <b>L</b> U | output impedance                        | 20-20kHz, I <sub>out</sub> =1A                 | <0.35                 | mΩ   |

<sup>1)</sup> Power is limited by overcurrent protection system (OCP)

Table 3 Audio Characteristics

<sup>2)</sup> Continuous output power depends on properties of the thermal system. With adequate thermal interface from the aluminum back plate to case / heatsink all power ratings are continuous power provided the aluminum backplate temperature is within recommended operating conditions. Data provided is based on module operating in free air.

<sup>3)</sup> THD @ 100W and DIM readings limited by analyzer

<sup>4)</sup> Kelvin (4-terminal) measurement on edge connector.

# 1.4 Typical Audio Performance, Graphs

$T_A$ =25° free operating air, 20kHz AES17 filter (AP), typical operating conditions (Table 2) unless otherwise noted.

Figure 1 THD [dB] vs. Frequency @  $4\Omega$

Figure 2 THD+N[dB]vs. Power @ f=1kHz

Figure 3 Frequency Response @  $V_i$ =2.83V

sales@purifi-audio.com (1.00) December 2024

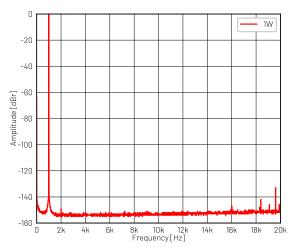

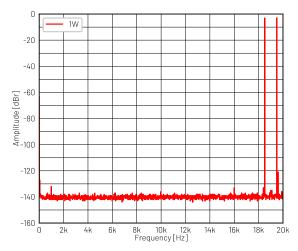

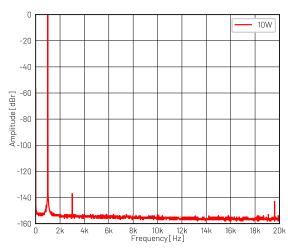

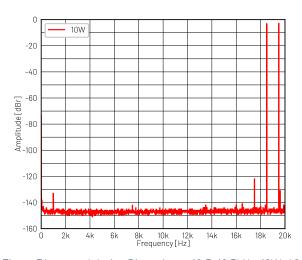

$T_A=25^{\circ}$  free operating air, 20kHz AES17 filter (AP), 16K/48kHz/32x avg. FFT's, Equiripple window, typical operating conditions (Table 2) unless otherwise noted.

Figure 4 Frequency Spectrum (FFT) @ 1kHz, 1W, 4Ω

Figure 5 Intermodulation Distortion @ 18.5+19.5kHz, 1W,  $4\Omega$

Figure 6 Frequency Spectrum (FFT) @ 1kHz, 10W,  $4\Omega$

Figure 7 Intermodulation Distortion @ 18.5+19.5kHz, 10W,  $4\Omega$

Figure 8 Frequency Spectrum (FFT)@ 1kHz, 100W,  $4\Omega$

Figure 9 Intermodulation Distortion @ 18.5+19.5kHz, 100W,  $4\Omega$

6

$T_A$ =25° free operating air, 20kHz AES17 filter (AP), typical operating conditions (Table 2) unless otherwise noted.

Figure 12 Power Stage Efficiency vs. Output Power

Output Power[W]

Output Power[W] Figure 13 Power Stage Loss vs. Output Power (one channel)

250

Figure 14 Voltage Clipping/Recovery (behavior)

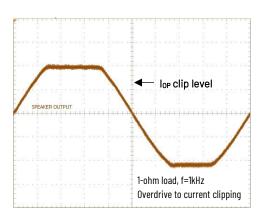

Figure 15 Current Clipping/Recovery (behavior)

# 1.5 Electrical Characteristics

Typical operating conditions (Table 2), f=1kHz, unless otherwise noted.

| . , prodrope                            | rating conditions (Table 2), f=1kHz, unless of<br><b>Parameter</b> | 1.10111100110                         | Condition                | .0               | Min                                    | Typ <sup>1)</sup> | May      | Unit             |

|-----------------------------------------|--------------------------------------------------------------------|---------------------------------------|--------------------------|------------------|----------------------------------------|-------------------|----------|------------------|

| 0                                       |                                                                    |                                       | Condition                | S                | MIN                                    | тур"              | Max      | Unit             |

|                                         | onsumption & Efficiency                                            | / \/D \/                              | 2)                       |                  |                                        | 10                |          |                  |

| I <sub>VP</sub>                         | Power Stage supply, current                                        | (+VP,-VF                              |                          |                  |                                        | 12                |          | mΑ               |

| I <sub>DR</sub>                         | Gate Drive supply, current                                         |                                       | ormal operation          |                  |                                        | 50                |          | mΑ               |

| I <sub>OP</sub>                         | OPAMPs supply, current                                             | (+VOP, -VOP), Normal operation        |                          |                  | 25                                     |                   | mΑ       |                  |

| $I_{VD}$                                | uC and logic supply, current                                       |                                       | rmal operation           |                  |                                        | 7.5               |          | mΑ               |

| • • • • • • • • • • • • • • • • • • • • | ao ana iogio oappiy, oan one                                       |                                       | plifier not switch       | ning             |                                        | 2.5               |          | mΑ               |

| n                                       | Efficiency                                                         | $R_L=8\Omega$                         |                          |                  |                                        | 96                |          | %                |

| η                                       | Littlefiley                                                        | $R_L$ = 4 $\Omega$ , Full rated power |                          |                  | 94                                     |                   | %        |                  |

| Audio Inpu                              | ıts & Output                                                       |                                       |                          |                  |                                        |                   |          |                  |

|                                         |                                                                    | Differen                              | tial, pos. to neg.       | input            |                                        | 2.2               |          | kΩ               |

|                                         |                                                                    | Single-e                              | nded, input to Gi        | ND, positive     |                                        | 5.2               |          | kΩ               |

| $R_{in}$                                | Input impedance                                                    | input (IN                             |                          |                  |                                        | 5.2               |          | KU               |

|                                         |                                                                    |                                       | nded, input to Gi        | ND, negative     |                                        | 1.1               |          | kΩ               |

|                                         |                                                                    | input (IN                             | -)                       |                  |                                        |                   |          |                  |

| Av                                      | Voltage Gain                                                       | V <sub>0</sub> /V <sub>1</sub>        |                          |                  | 12.3                                   |                   | dB       |                  |

| V <sub>in_1%THD</sub>                   | Differential input voltage                                         |                                       | %THD @ $R_L = 4\Omega$ , | VP=±65V 1)       |                                        | 10.8              |          | V <sub>rms</sub> |

| CMRR                                    | Common Mode Rejection Ratio                                        |                                       | put, 1kHz                |                  |                                        | >60               |          | dB               |

| PSRR                                    | Power Supply Rejection Ratio                                       |                                       | Vrms f≤1kHz ripp         | ole, either rail |                                        | >90               |          | dB               |

| $ V_{oDC} $                             | Speaker Output, DC offset                                          | Grounde                               | ed analog inputs         |                  |                                        | <10               |          | mV               |

|                                         |                                                                    | ldle (indi                            | cative)                  |                  |                                        | 550               |          | kHz              |

| fs                                      | Switching frequency                                                | Positive clipping                     |                          |                  |                                        | >50               |          | kHz              |

|                                         |                                                                    | Negative clipping                     |                          | 0                |                                        |                   | Hz       |                  |

| Logic Con                               | trol Signals                                                       |                                       |                          |                  |                                        |                   |          |                  |

| V <sub>IH</sub>                         | High level input threshold                                         | (/AMPON)                              |                          | 2.7              |                                        |                   | V        |                  |

| VIL                                     | Low level input threshold                                          |                                       |                          |                  |                                        | 0.65              | V        |                  |

| VIH_I2C                                 | High level input threshold                                         |                                       |                          | 2.3              |                                        | 0.00              | V        |                  |

| V <sub>IL_I2C</sub>                     | Low level input threshold                                          | (SDA)                                 |                          | 2.0              |                                        | 1                 | V        |                  |

| VILLIZC                                 | High level output voltage                                          |                                       |                          | I=6mA            | 2.6                                    |                   |          | V                |

|                                         | Low level output voltage                                           | (SDA)                                 | Onen drain               | I=10mA           | 2.0                                    |                   | 0.6      | V                |

| V <sub>OL_I2C</sub>                     | · · · · · ·                                                        | (SDA)                                 | Open-drain               | I=IUMA           |                                        |                   | 10       | -                |

| I <sub>OL_I2C</sub>                     | Low level sink current                                             |                                       |                          |                  | 1.05                                   |                   | 10       | mΑ               |

| VIHLSCL                                 | _                                                                  |                                       |                          |                  | 1.65                                   |                   | 0.5      | V                |

| V <sub>IL_SCL</sub>                     | Open collector input                                               | (SCL)                                 | CL)                      |                  |                                        |                   | 0.5      | V                |

| I <sub>IH_SCL</sub>                     | _                                                                  |                                       |                          |                  |                                        |                   | 1        | mΑ               |

| lil_SCL                                 |                                                                    |                                       |                          |                  |                                        |                   | 1<br>10  | mΛ               |

| V <sub>ooc</sub>                        | Open collector output                                              | (/FATAL                               | )                        |                  |                                        |                   | 10<br>65 | mA<br>V          |

|                                         | Link lovel even three en                                           |                                       |                          |                  | \(\(\D\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                   | 00       | V                |

| V <sub>OH</sub>                         | High level output voltage                                          | (READY,                               | PSUDIS)                  |                  | VD-0.7 <sup>2)</sup>                   | 5                 | 0.0      |                  |

| V <sub>OL</sub>                         | Low level output voltage                                           |                                       |                          |                  |                                        |                   | 0.6      | V                |

| Protection                              |                                                                    |                                       |                          |                  |                                        |                   |          |                  |

| locp                                    | Overcurrent Protection, threshold                                  | Current                               |                          |                  |                                        | 25                |          | А                |

| f <sub>DCP</sub>                        | DC Protection, Speaker terminal                                    |                                       | on filter corner fr      |                  |                                        | 2.5               |          | Hz               |

| VDCP                                    | <u>'</u>                                                           |                                       | limit, low-pass fi       |                  |                                        | 12                |          | V                |

| Тотр                                    | Thermal Protection, Heatsink                                       | Over-temperature, 2°C hysteresis      |                          |                  | 75                                     |                   | °C       |                  |

| Tutp                                    | ,                                                                  | Under-temperature, 2°C hysteresis     |                          |                  | 0                                      |                   | °C       |                  |

| OVP <sub>VP</sub>                       | <b>-</b>                                                           |                                       | P), 1V hysteresis        |                  |                                        | 75                |          | V                |

| OVP <sub>DR</sub>                       | Overvoltage Protection, threshold                                  |                                       | .5V hysteresis           |                  |                                        | 17.5              |          | V                |

| OVP <sub>OP</sub>                       |                                                                    |                                       | VOP), 0.5V hyste         | resis            |                                        | 18                |          | V                |

| UVP <sub>VP</sub>                       | <del> </del>                                                       |                                       | ), 1V hysteresis         |                  |                                        | 32                |          | V                |

| UVPDR                                   | Undervoltage Protection, threshold                                 |                                       | .5V hysteresis           |                  |                                        | 13                |          | V                |

| UVPOP                                   |                                                                    | (+VOP, -VOP), 0.5V hysteresis         |                          |                  |                                        | 11                |          | V                |

<sup>1)</sup> Performance depends on physical implementation and system-level circuitry/configuration. Data provided is based on module operating in free air. 2) If 5V > VD > +VOP, VoH min will be VD-0.7V

Table 4 Electrical Characteristics

# 1.6 Timing Characteristics

Typical operating conditions unless otherwise noted.

|             | Parameter                             | Conditions                             | Min Typ <sup>1)</sup> | Max | Unit |

|-------------|---------------------------------------|----------------------------------------|-----------------------|-----|------|

| Control Sig | nals                                  | •                                      |                       |     |      |

| /AMPON      | Mute time                             | Pin asserted high to Amp output HiZ    | 1                     |     | ms   |

| TAMPON      | Un-mute time                          | Pin asserted low to Amp output LoZ     | 1.25                  |     | ms   |

| READY       | Start delay                           | Supplies stable to READY asserted high | 1.25                  |     | ms   |

| /FATAL      | Amplifier failure to signal assertion | Failure to /FATAL low                  | 40                    |     | ms   |

| PSUDIS      | PSU off signal                        | DC failure to PSUDIS high              | 40                    |     | ms   |

| HS/ADDR     | Mode Selection                        | Power-up to Mode latched               | 10                    |     | ms   |

| Protection  | Systems                               |                                        |                       |     |      |

| tocp        | OCP Mute cycle duration               | OCP event to reenable outputs          | >300                  |     | ns   |

| OLP         | Overload Protection, threshold        | Ratio of OCP cycles to non-OCP cycles  | 12                    |     | %    |

| tolp        | OLP Mute cycle duration               | OLP even to reenable outputs           | 1                     |     | S    |

| tDCP        | DCP Mute cycle duration               | DCP even to reenable outputs           | 1                     |     | S    |

<sup>1)</sup> Performance depends on physical implementation and system-level circuitry/configuration. Data provided is based on module operating in free air.

Table 5 Timing Characteristics

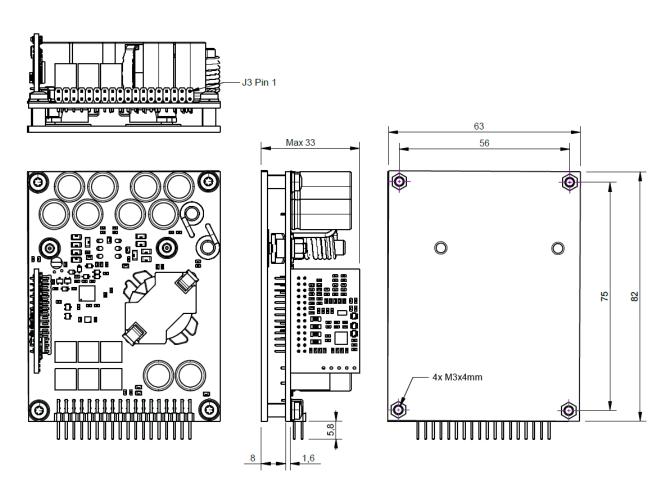

# 1.7 Mechanical Characteristics

| Parameter              |                                     | Conditions             | Min | Тур | Max | Unit |

|------------------------|-------------------------------------|------------------------|-----|-----|-----|------|

|                        | Length                              |                        |     | 82  |     | mm   |

| SIZE                   | Width                               |                        |     | 63  |     | mm   |

|                        | Height                              |                        |     | 33  | 36  | mm   |

|                        | Threaded standoff, heatsink-PCB, M3 | Height                 |     | 6   |     | mm   |

|                        | Threaded stud, heatsink-FET-PCB     | Length                 |     | 13  |     | mm   |

| Mounting <sup>1)</sup> | Spacer, FET-PCB, M3                 | Height                 |     | 3   |     | mm   |

| Mounting"              |                                     | Diameter               |     | M3  |     | -    |

|                        | Threaded standoff                   | Available thread depth |     |     | 4   | mm   |

|                        |                                     | Torque                 |     | •   | 0.5 | Nm   |

<sup>1)</sup> The aluminum back plate is connected to GND and can be mounted electrically in contact with chassis GND. Do not use the aluminum back plate/threaded mounting holes for power supply connection.

Table 6 Mechanical Characteristics

## 2 Introduction

The 1ET6525SA is a single-channel, ultra-high-performance, analog-input Class D amplifier module capable of delivering over 450W of power. It sets a new benchmark for audio quality across all amplifier classes. By leveraging 2<sup>nd</sup> generation Eigentakt ErrorCorrection, it achieves the highest level of performance. Its compact size and exceptional reliability make it suitable for a wide range of applications, while its superior sound quality makes it the clear choice for applications where audio excellence is paramount.

PURIFI's ongoing research in nonlinear control theory has led to the development of the first mathematically precise large-signal model for self-oscillating amplifier controllers. This breakthrough enables the complete optimization of the feedback circuit, resulting in performance improvements of at least an order of magnitude over existing designs. Additionally, the amplifier module features a comprehensive protection system, ensuring robustness and ease of integration.

These circuits and methods provide many practical and audible benefits:

# • High loop gain (>85dB) in the entire audio band (2<sup>nd</sup> generation Eigentakt ErrorCorrection)

This figure corresponds to an unprecedented 356MHz Gain-Bandwidth Product and produces consistent ultra-high performance across the audio spectrum unmatched by audio amplifiers of any technology or operating class.

## Negligible intermodulation distortion (IMD)

o A very good measure for how well an amplifier handles complex signals. Sonically low IMD means a highly resolved and stable stereo image across the whole spectrum, even during very complex and busy passages.

#### THD remains extremely low at any frequency and any power level right until clipping

o Translates into a total lack of sonic signature, and an ability to reproduce any type of music without preference for genre or production style.

#### • Negligible output noise

o No audible noise. Deep black silence and a generous and detailed sound even at very low playback volumes.

# • High power supply rejection ratio (PSRR)

• The module places no particular demands on the power supply quality. A simple off-the-shelf unregulated SMPS will not degrade audio performance.

#### • Load-invariant frequency response and negligible output impedance

The amplifier handles difficult loudspeakers with ease, including those that challenge most other amplifiers.

#### Controlled, second-order low-pass response

- Very flat audio-band response with a sensible, 80kHz bandwidth.

- o Reduced sensitivity to out-of-band noise from DACs, reducing the requirements on the DAC reconstruction filter. This leaves a shorter signal path between DAC and loudspeaker.

- o Problem-free operation with outboard DACs over which you may have no control.

#### Very low idle losses and reduced electromagnetic interference (EMI)

- o The enormous loop gain allows relaxed timing of the power MOSFETs without degrading audio performance.

- o Idle losses are minimized.

- o Very little to no effort needed to pass regulatory tests.

# • Exceptionally clean clipping and clipping-recovery in both voltage and current domains

Clips cleanly and recovers immediately without "overhang". Current limiting is equally instantaneous and glitch free. This guarantees the smallest amount of audible artefacts when pushed into clipping or overload protection.

## • Overall implementation/integration ease saves time and cost for the system integrator

o Architecture completely eliminates heterodyning in multichannel applications.

# 3 Overview

# 3.1 Edge Connector, J3

| Pin                 | Signal    | Rating   | 1/0 | Description                                                           |  |  |  |  |

|---------------------|-----------|----------|-----|-----------------------------------------------------------------------|--|--|--|--|

| Power Supp          | olies     | <u> </u> |     |                                                                       |  |  |  |  |

| 1, 2                | +VP       |          | Р   | Power Stage Supply, positive rail                                     |  |  |  |  |

| 3,4,5               | GND       |          | _   | Ground                                                                |  |  |  |  |

| 6,7,8               |           |          |     |                                                                       |  |  |  |  |

| 9,10                | -VP       |          | Р   | Power Stage Supply, negative rail                                     |  |  |  |  |

| 11                  | VDR       | Table 2  | Р   | Gate Drive Supply, referenced to -VP                                  |  |  |  |  |

| 12                  | VD        |          | Р   | (optional use) External Voltage supply to on-board 5V regulator       |  |  |  |  |

| 26                  | +VOP      |          | Р   | OPAMPs, positive rail                                                 |  |  |  |  |

| 25                  | -VOP      |          | Р   | OPAMPs, negative rail                                                 |  |  |  |  |

| 27                  | GND       |          | -   | Ground                                                                |  |  |  |  |

| I/O's               |           |          |     |                                                                       |  |  |  |  |

| 13,14,15,           | OUT-      |          | 0   | Speaker Output, negative (internally connected to GND)                |  |  |  |  |

| 16,18               | 001       |          | U   | Speaker output, negative (internally connected to one)                |  |  |  |  |

| 20,21,22,           | OUT+      |          | 0   | Speaker Output, positive                                              |  |  |  |  |

| 23,24               | 001       |          | Ŭ   | opeanor output, poortive                                              |  |  |  |  |

| 17, 19,<br>28,33,34 | NC        |          | -   | Not connected                                                         |  |  |  |  |

| 29                  | IN+       |          | -   | Analog Input, positive                                                |  |  |  |  |

| 30                  | IN-       | Table 2  | I   | Analog Input, negative                                                |  |  |  |  |

| 31                  | HS/ADDR   |          | I   | Mode/I2C Address Selection; set by one 1% resistor.                   |  |  |  |  |

| 70                  | PSUDIS    |          | 0   | PSU off control signal (SW Mode), or                                  |  |  |  |  |

| 32                  | /AMPON    |          | 1   | Amplifier Disable (HW Mode) – pull low to enable Amp                  |  |  |  |  |

| 7.5                 | SDA       |          | I   | I2C Data (SW Mode), or                                                |  |  |  |  |

| 35                  | READY     |          | 0   | Amplifier Ready (HW Mode) - "all good for operation" when high        |  |  |  |  |

| 36                  | SCL       |          | I   | I2C clock (SW Mode), or                                               |  |  |  |  |

| J0                  | /FATAL    |          | 0   | Amplifier "error/fail" (HW Mode) – signal goes low on error           |  |  |  |  |

| Aluminum E          | Backplate |          |     |                                                                       |  |  |  |  |

|                     | GND       |          | _   | Ground. Do not use the aluminum backplate to connect power supply GND |  |  |  |  |

|                     | טויוט     |          | _   | connections                                                           |  |  |  |  |

Table 7 Edge Connector, J3

sales@purifi-audio.com (1.00) December 2024

# 4 Power Supply, Control Signals & I/O's

# 4.1 Power Supply

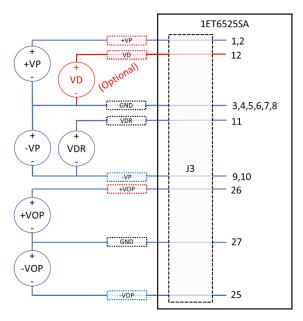

Refer to below figure showing required power supplies and how to connect these to 1ET6525SA:

Figure 17 Power Supplies

Voltage, current and power ratings are described in detail in Table 2 Recommended Operating Conditions and Table 4 Electrical Characteristics.

#### 4.1.1 Power Stage Supply (+VP, -VP)

1ET6525SA requires a ground-centered split-rail supply for the amplifier output stage.

Multiple factors need to be considered when determining capabilities of this supply, e.g., peak/continuous audio power requirements, nominal/minimum (speaker) load, thermal constraints and time constants/durations etc.

Refer to Figure 10 to determine required DC voltage based on desired nominal output power.

For a given supply voltage and output power specification, the power supply peak power and peak current can be estimated:

$$P_{psu\_peak} = 2 \frac{P_{out\_rms}}{\eta}$$

;  $I_{psu\_peak} = \frac{P_{psu\_peak}}{VP}$

The supply should be designed such that each rail has enough thermal headroom to drive full peak power for a minimum of one half-period of the lowest desired audio frequency or as otherwise required for continuous power delivery as determined by the system integrator. The 1ET6525SA design limits power delivery only if OCP or OTP events are triggered and in practice, especially in multichannel applications, the power supply often is the limiting factor for sustained power delivery.

sales@purifi-audio.com (1.00) December 2024

Although 1ET6525SA includes over- and under-voltage protection (OVP/UVP) the power supply designer should pay close attention to managing "supply pumping". As example, by either ensuring that the supply can sink current or by utilizing enough electrolytic energy storage to keep rail voltages within recommended operating range in all use situations. In a stereo/multichannel application it is recommended to alternate the phase of channels such that PSU rails are loaded as balanced as possible. However, this alone is not enough remedy to always avoid supply pumping and it is the responsibility of the system integrator to define and ensure adequate levels of caution.

## 4.1.2 Gate Drive Supply (VDR)

1ET6525SA requires an external supply for the gate drive circuitry. It is essential that the supply is designed as a floating rail, that must be referenced to -VP.

VDR directly feeds the low-side gate driver; the design utilizes boot-strap circuitry to create a rail relative to high-side driver.

#### 4.1.3 OPAMPs Supply (+VOP, -VOP)

1ET6525SA requires an external ground-centered split-rail supply for the modulator and general analog low-power circuitry. There are no particular design constraints outside of normal audio design best-practice.

#### 4.1.4 (optional) Digital Supply (VD)

The module includes a voltage regulator for the digital supply, sourced by +VOP and therefore does not require an external power supply for the digital section. To communicate with the module via I2C when the op amp supplies are powered down, VD can be connected to an external 5V supply that will supply the on-board microcontroller.

#### 4.1.5 Power Supply Sequencing

1ET6525SA monitors all supplies <u>with the exception of the optional VD supply</u> and prevents operation unless all supply voltages are within preset safe thresholds.

sales@purifi-audio.com (1.00) December 2024

# 4.2 Control Signals

#### 4.2.1 PSUDIS & /AMPON

Signals share the same physical net and adapt function according to Operation mode (refer to section 5).

The net is tied directly to a microcontroller GPIO pin and has a  $27k\Omega$  pull-up to 5V.

#### 4.2.2 SCL & /FATAL

Signals share the same physical net and adapt function according to Operation mode (refer to section 5).

The signal is connected to the collector of a transistor which has the emitter tied to a uC GPIO pin and the base tied permanently to 5V via a 3.3k $\Omega$  resistor.

As SCL, the transistor will level-shift the incoming signal to levels suitable for the uC.

As /FATAL, the transistor will pass output from the microcontroller and function as open-collector output.

#### 4.2.3 SDA & READY

Signals share the same physical net and adapt function according to Operation mode (refer to section 5).

The net is tied directly to a microcontroller GPIO pin.

As SDA, the signal is a bi-directional (open-drain) I/O and complies with the general I2C specification in terms of levels and timing.

As READY, the signal is configured as CMOS-level compliant logic output.

sales@purifi-audio.com (1.00) December 2024

## 4.3 Audio Inputs & Output

#### 4.3.1 Audio Input (IN+, IN-)

1ET6525SA has a differential analog input.

The behavior of the input can be described as equivalent to a traditional differential op-amp configuration with gain and input resistance as listed in Table 4.

For best performance specs the overall amplifier gain is kept reasonably low. If desired, a separate gain stage can be implemented upstream to 1ET6525SA. It is up to the system integrator to specify the properties of any pre-gain/signal-conditioning circuitry as well as test how it affects the rest of the system.

Adjusting the 1ET6525SA input resistors voids all performance specifications and should therefore be avoided.

Amplifier clipping is a function of supply voltage (VP), amplifier gain and audio input voltage. As example, in nominal operating conditions (see Table 2) a balanced analog input of 10.8Vrms sine is required for the output to produce a signal with ~1%THD indicating the point where the amplifier is close to clipping.

#### 4.3.2 Speaker Output (OUT+, OUT-)

1ET6525SA has a single-ended ground-centered speaker output.

The system integrator might notice that the OUT- terminal is connected to GND and be tempted to route the negative speaker terminal to GND elsewhere in the system. This, however, should be avoided as the internal feedback connections sense the voltage between OUT+ and OUT- terminals. Best performance is achieved by treating the speaker outputs as a balanced pair.

Bridging two 1ET6525SA modules may result in performance degradation as the circuit is not configured to sense the voltage differential that exists between the (now unused) OUT- terminals of the two 1ET6525SA designs. Bridging is therefore not recommended, and all operation and performance specs are void in this configuration. It should be noted that while the amplifier protection systems remain fully intact in a bridged configuration, it is not possible for the individual half-bridges (modules) to detect a DC across the speaker load (i.e. between two modules).

sales@purifi-audio.com (1.00) December 2024

# 5 Operating Modes & Status Reporting

1ET6525SA can operate in two modes:

1. HW Mode: all control via pins (HW interface)

2. SW Mode: enables I2C control (I2C interface)

Modes are selected via resistor value programming, please see Table 8

# 5.1 Mode Selection (HS/ADDR Settings)

The programming resistor must be connected between the HS/ADDR pin and GND. Setting of the HS/ADDR signal defines operation mode and I2C address per following table:

| Mode           | I2C Address | Resistor: HS/ADR to GND |

|----------------|-------------|-------------------------|

| Hardware Mode  | -           | ∞<br>(not populated)    |

|                | 0x50        | 0                       |

|                | 0x51        | 1K9                     |

|                | 0x52        | 3K9                     |

|                | 0x53        | 6K8                     |

|                | 0x54        | 10K                     |

|                | 0x55        | 12K                     |

|                | 0x56        | 18K                     |

| Software Mode  | 0x57        | 22K                     |

| 55141141511645 | 0x58        | 27K                     |

|                | 0x59        | 33K                     |

|                | 0x5A        | 47K                     |

|                | 0x5B        | 56K                     |

|                | 0x5C        | 82K                     |

|                | 0x5D        | 120K                    |

|                | 0x5E        | 190K                    |

|                | 0x5F        | 390K                    |

<sup>\*)</sup> Resistors must be 1% or better.

Table 8 Mode Selection via HS/ADDR

#### 5.2 HW Modes

In HW Mode the channel controller monitors and operates all available circuits for environmental checks (Over/Under-voltage, Temperature) and all protection circuits (Current limiting, Overload protection, DC protection, Frequency protection and Bootstrap refresh).

Status and control information are accessible via three signals (nets):

| NET   | Signal | Rating  | 1/0 | Description                                          |

|-------|--------|---------|-----|------------------------------------------------------|

| J3,32 | /AMPON |         | - 1 | Amplifier Disable – pull low to enable Amp           |

| J3,25 | READY  | Table 2 | 0   | Amplifier Ready – "all good for operation" when high |

| J3,36 | /FATAL |         | 0   | Amplifier "error/fail" – signal goes low on error    |

Table 9 Status/Control signals in HW Mode

#### 5.3 SW Mode

The main feature of the SW Mode is access via I2C to a vast amount of status and control information.

I2C is accessed via SCL, SDA.

In addition to status/control information accessible via I2C, one hardwired output signal (PSUDIS) is available.

|   | Pin   | Signal | Rating  | 1/0 | Description            |

|---|-------|--------|---------|-----|------------------------|

|   | J3,32 | PSUDIS |         | 0   | PSU off control signal |

| Ī | J3,35 | SDA    | Table 2 | - 1 | I2C Data               |

| ĺ | J3,36 | SCL    |         | - 1 | I2C clock              |

Table 10 Status/Control signals in SW Mode

#### 5.3.1 PSUDIS (GPIO)

PSUDIS is essentially a GPIO which can be configured via the I2C register. Per default, GPIO is set to echo the AmpFail flag and is intended to be used to control the power supplies on and off.

It is possible to force the GPIO (i.e., SMPS\_OFF) high or low via the I2C register – this enables control of the power supplies via the amplifier I2C interface.

|   | GPIODir | DPI0Val | GPIOAmpFail | Description                            |

|---|---------|---------|-------------|----------------------------------------|

|   | 0       | 0       | 0           | GPIO is forced low                     |

| Ī | 0       | 1       | 0           | GPIO is forced high                    |

| Ī | 1       | X       | 0           | Reserved                               |

| Ī | Х       | X       | 1           | GPIO echoes the AmpFail flag (default) |

Table 11 PSUDIS (GPIO) mapping

# 5.4 I2C Register Map

| Reg          | Name                     | Data type                     | R/W    | Description                                                                                |

|--------------|--------------------------|-------------------------------|--------|--------------------------------------------------------------------------------------------|

|              | Channel count            | High Nibble                   | R      | 1 = module has one active channels                                                         |

| 0x00         | Product Type             | Low Nibble                    | R      | 1 = amplifier module                                                                       |

| 0x01         |                          | last a su a s                 |        | 0x19 0x107D 0F0F(4) #0F1/ 0FA// *** 4x4-                                                   |

| 0x02         | Power                    | Integer                       | R      | 0x7D 0x197D = 6525 (dec) = "65V, 25A" module                                               |

| 0x03         | Version                  | High Nibble                   | R      | Hardware revision number                                                                   |

| UXUS         | Revision                 | Low Nibble                    | R      | Hardware sub-revision number                                                               |

| 0x04<br>0x05 | Serial                   | Integer                       |        | Serial number (convert hex to dec to get serial number)                                    |

| 0x06         | Firmware                 | High Nibble                   | R      | Firmware revision number                                                                   |

| 0x07         | 1 II II I Wale           | Low Nibble                    | R      | Firmware sub-revision number                                                               |

|              | Reserved                 | -                             | -      |                                                                                            |

| 0x08         | Reserved                 | -                             | -      |                                                                                            |

|              | Reserved                 | Bits 7-4                      | -      |                                                                                            |

|              | GPI0AmpFail              | Bit 3                         | W      | Set to make pin high when AmpFail is high, and Hi-Z otherwise                              |

| 0x09         | GPIODir                  | Bit 2                         | W      | Set low for using GPIO feature                                                             |

|              | GPIOVal                  | Bit 1                         | W      | GPIO pin value                                                                             |

|              | AmpEnable                | Bit 0                         | W      | Request to turn on amplifier                                                               |

|              | Reserved                 | Bits 7-3                      | -      |                                                                                            |

| 0x0A         | ICLIP                    | Bit 2                         | R      | Flags that current limiting has happened since this flag was last read                     |

| 07.07.       | VCLIP                    | Bit 1                         | R      | Flags that at clipping has happened at least once since this flag was last read            |

|              | AmpReady                 | Bit 0                         | R      | Power stage is switching and passing signal                                                |

|              | Reserved                 | Bit 7                         | -      |                                                                                            |

|              | AmpFail                  | Bit 6                         | R      | Flags that DC at the output persisted after turning the power stage off                    |

|              | OverTemp                 | Bit 5                         | R      | Temperature too high.                                                                      |

| 0x0B         | MinV0P0ver               | Bit 4                         | R      | Negative op-amp supply too high.                                                           |

|              | PlusV0P0ver              | Bit 3                         | R      | Positive op-amp supply too high.                                                           |

|              | VDROver                  | Bit 2                         | R      | VDR too high.                                                                              |

|              | MinHVOver                | Bit 1                         | R      | Negative high-voltage supply too high.                                                     |

|              | PlusHV0ver               | Bit 0                         | R      | Positive high-voltage supply too high.                                                     |

|              | Reserved                 | Bits 7-6                      | -      | T                                                                                          |

|              | UnderTemp                | Bit 5                         | R      | Temperature too low.                                                                       |

| 000          | MinVOPUnder              | Bit 4                         | R      | Negative op-amp supply too low.                                                            |

| 0x0C         | PlusVOPUnder<br>VDRUnder | Bit 3                         | R      | Positive op-amp supply too low.                                                            |

|              | MinHVUnder               | Bit 2<br>Bit 1                | R<br>R | VDR too low.                                                                               |

|              | PlusHVUnder              | Bit 0                         | R      | Negative high-voltage supply too low.                                                      |

|              |                          | Bits 7-2                      | K      | Positive high-voltage supply too low.                                                      |

| 0x0D         | Reserved OverloadError   | Bit 1                         | R      | Dower stage is temperarily turned off ofter a quetained everywrent event                   |

| UXUD         | DCError                  | Bit 0                         |        | Power stage is temporarily turned off after a sustained overcurrent event                  |

| 0,00         | PlusVP                   |                               | R      | Power stage is temporarily turned off after DC was detected on the output.                 |

| 0x0E<br>0x0F | MinVP                    | Unsigned short Unsigned short | R<br>R | Measured positive high-voltage rail in volts  Measured negative high-voltage rail in volts |

| 0x0F<br>0x10 | VDR                      | Unsigned short                | R      | Measured VDR in decivolts.                                                                 |

| 0x10         | Temperature              | Signed short                  | R      | Measured temperature in °C                                                                 |

| 0x11         | DC                       | Signed short                  | R      | Measured output DC in volts                                                                |

| 0x12<br>0x13 |                          |                               |        | ·                                                                                          |

| 0x13<br>0x14 | Fsw                      | Unsigned int                  | R      | Measured switching frequency in units of 250Hz.                                            |

| 0x15         | PlusVOP                  | Unsigned short                | R      | Measured positive op amp supply, in decivolts                                              |

| 0x16         | MinVOP                   | Unsigned short                | R      | Measured negative op amp supply, in decivoits                                              |

| 0x17         |                          | Strongthou offort             |        | 1.0000.00                                                                                  |

| 0x1F         | Reserved                 | -                             | -      |                                                                                            |

|              |                          |                               |        |                                                                                            |

Table 12 I2C Register Map

# 6 Protection System

1ET6525SA is protected from overload and failure by means of several protection circuits. All systems are continuously active while the amplifier is powered and operating.

#### 6.1 Environmental checks

Environmental checks denote circuits that monitor operating conditions maintained or affected by external sources or influences such as power supply voltages and ambient/system temperatures.

Environmental checks are enabled in both HW Mode and SW Mode.

#### 6.1.1 Over/Under-Voltage Protection, +VP, -VP, VDR, +VOP, -VOP

The high voltage supply rails (Power Stage Supply) must be within certain thresholds for safe operation. If supply levels are outside min-to-max thresholds denoted in table below the Amplifier power stage output is brought immediately into high-impedance state (HIZ).

In HW Mode an OVP/UVP condition asserts the READY signal low. It is recommended that the system host monitors this signal.

In SW Mode OVP/UVP states are reported in the I2C register with a great deal of associated information available, please refer to the I2C register map for details.

#### 6.1.2 Temperature Protection, Backplate

1ET6525SA utilizes circuitry to monitor the temperature of the required aluminum back plate (used for cooling the FET's) and take appropriate action conditions are outside recommended operating range.

An OTP/UTP condition brings the amplifier output into high-impedance state (stop switching). Normal operation automatically resumes once temperatures return within the tolerable range and no involvement from user or system host controller is required.

In Hardware Mode an OTP/UTP condition asserts the READY signal low for as long as the temperature is out of tolerable range. It is recommended that the system host monitors this signal.

In Software Mode OTP/UTP status and actual measured temperature are reported in the I2C register, please refer to the register map for additional information.

## 6.2 Overcurrent Protection (OCP)

Each amplifier channel is protected against short- and long-term high-current overload.

A system monitors the output stage current and abruptly engages a *protection cycle* (*OCP cycle*) if a pre-set overcurrent threshold is exceeded. During a *protection cycle* the power stage output is flipped, i.e., if the overcurrent event concerns the high-side FET the half-bridge output will be force low, and reversely, if the overcurrent event concerns the low-side FET the half-bridge will be forced high. The duration of a *protection cycle* is approximately ~300nS or until the output current has decreased below a safe threshold. The combined behavior of the OCP circuit is comparable to a current-limiter function.

Extended current-limiting can result in triggering of the Overload Protection (refer to section 6.3).

Following a *protection cycle*, normal operation is automatically resumed and no involvement from user or system host controller is required.

OCP is enabled in all modes of operation (SW Mode, HW Mode).

OCP is reported in the I2C register (ICLIP) when operating in SW Mode.

# 6.3 Overload Protection (OLP)

To safeguard the Module against continuous operation at the OCP threshold (current-limiting) a circuit keeps track of OCP cycles as function of time. If the amplifier is running in current-limiting more than approximately 12% over time an OLP mute cycle is triggered. In events of continuous OCP the OLP triggers after approximately 10ms. During a mute cycle the output stage is disabled (left in high-impedance state) approximately 1 second.

Following a *mute cycle*, normal operation is automatically resumed and no involvement from user or system host controller is required.

OLP is enabled in all modes of operation (SW Mode, HW Mode).

OLP is reported in the I2C register (OverloadError) when operating in SW Mode.

## 6.4 DC Protection (DCP)

The amplifier audio signal channel is capable of passing DC signals, i.e., the audio channel does not include any form of low-cut (high-pass) filtering. To protect the speaker against potentially harmful DC signals 1ET6525SA includes a circuit that monitors the speaker output and disables the power stage should certain conditions be exceeded. The speaker output signal is low-pass filtered with a corner frequency below the audible range and if the filtered signal exceeds a preset threshold a DCP mute cycle is triggered (Table 4).

Following a *mute cycle*, normal operation is automatically resumed <u>only</u> if the DC is reduced within safe thresholds. If so, no involvement from user or system host controller is required. However, if DC persists at the end of the *mute cycle*, the power stage is latched off and will stay off until the user or system host controller takes deliberate action to restart operation.

DCP is enabled in SW Mode and HW Mode.

DCP-latch-off condition is reported in the I2C register (AmpFail) when operating in SW Mode. Note that a DCP mute cycle is not reported.

It is recommended to frequently poll the AmpFail flag and control the power supply accordingly. Alternatively, program the GPIO pin to output the state of AmpFail flag (default mode) and use that to shut down the power supply in case of a failure.

In HW Mode, DCP-latch-off condition asserts /FATAL signal low. It is recommended that the /FATAL signal is used to switch off the power supplies.

# 7 Mechanical Specifications & System Considerations

# 7.1 Module Dimensions

Figure 18 Dimensions

sales@purifi-audio.com (1.00) December 2024

## 7.2 Thermal Requirements

While the 1ET6525SA boasts very low idle losses and high overall efficiency, proper cooling is crucial for maintaining sustained power delivery. To achieve the desired output power specifications, careful attention must be paid to the design of the thermal management system.

We recommend mounting the module on a heatsink, such as a well-designed aluminum chassis, and using a thermal interface material (e.g., thermal grease or pad) to optimize heat dissipation. This will ensure that the power stage operates efficiently while maintaining the desired ambient and heatsink temperatures.

# 7.3 Mechanical Requirements

Regarding the mechanical robustness of the final application, it is the responsibility of the system integrator to specify processes, materials, and locations for securing critical components, such as gluing, as needed. The system integrator must also prove and document both short- and long-term performance and reliability.

Ensuring the integrity of the mounting method and materials used to secure the module is crucial. We strongly recommend thoroughly testing the final product for robustness, including resistance to shock and vibration, to ensure reliable operation under all conditions.

# 7.4 Compliance Testing

1ET6525SA is designed with considerations for compliance of the end application. However, it is the responsibility of the system integrator to ensure any form of design-for-compliance and associated testing/certification which may be required.

# 8 Revision History

| Rev    | Date    | Description        | ID  |

|--------|---------|--------------------|-----|

| (0.90) | 2024-08 | Prerelease version | SP0 |

| (1.00) | 2024-12 | Final release      | KNM |

|        |         |                    |     |

|        |         |                    |     |

Table 13 Revision History

#### 1ET6525SA - Data Sheet